ПАИС - программируемая аналоговая интегральная схема (Field-programmable analog array) — набор базовых ячеек, которые могут быть сконфигурированы и соединены между собой для реализации наборов аналоговых функций: фильтров, усилителей, интеграторов, сумматоров, ограничителей, делителей, выпрямителей, и т. д. Особенностью схемы является полное или частичное изменение аналоговой схемы во время функционирования или изменение характеристик некоторых элементов схем (например, полосы пропускания или добротности фильтра).

Лидером в производстве ПАИС является компания Anadigm. Она производит два типа ПАИС:

Отличие из в том, что динамически конфигурируемая схема позволяет изменить полностью или частично функциональную структуру в работающем устройстве.

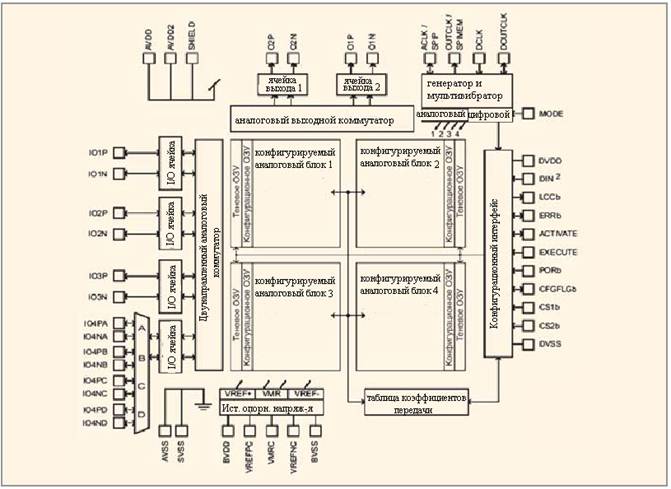

Структурная схема FPAA показана на рисунке.

Её основу составляют конфигурируемые аналоговые блоки (CAB), которые содержат наборы элементов для реализации стандартных устройств – операционных усилителей, компараторов, источников образцового напряжения, АЦП, а также конфигурационную память (LookkUp Table) и специальный интерфейс. Входные аналоговые сигналы подаются в CAB через конфигурируемые двунаправленные I/O ячейки. Ячейки I/O_Cell_1...3 осуществляют передачу сигнала напрямую в один из блоков. Ячейка I/O_Cell_4 содержит специальный мультиплексор, который позволяет подключать до 4 дифференциальных (или 8 несимметричных) входных сигналов или нагрузок (в режиме выходов). Каждый вход/выход ячейки может непосредственно подключаться к одному из блоков или предварительно обрабатываться при помощи набора стандартных устройств в любой комбинации: буферный усилитель, усилитель с программируемым коэффициентом усиления, программируемый фильтр, прецизионный усилитель со стабилизацией прерыванием. Выходные сигналы могут быть выведены из блоков на выводы I/O_Cell непосредственно или через дополнительные активные элементы, аналогично входным. Кроме того, выходные сигналы могут быть выведены напрямую через специальные выходные ячейки Output_Cell_1. ..2, которые также содержат программируемые фильтры и преобразователи дифференциальных сигналов в несимметричные. Эти ячейки можно использовать и для вывода цифровых сигналов с выходов компараторов. Синхронизация в ПАИС может осуществляться при помощи внешнего источника или от встроенного тактового генератора с внешним кварцевым резонатором. Частота внутреннего генератора может быть поделена четырьмя синхронными программируемыми делителями; каждая из частот может быть выведена на внешний выход. Режимы работы CAB, значения тактовых частот, направления передачи сигналов, назначения и конфигурация I/O_Cell, Output_Cell хранятся в так называемой конфигурационной памяти (Configuration SRAM). Копия содержимого конфигурационной памяти хранится в теневом ОЗУ (Shadow SRAM), которое может перезаписываться без нарушения процесса обработки сигнала. Архитектура ПАИС имеет простой и гибкий конфигурационный интерфейс. Он предназначен для работы как в автономном режиме, так и для связи с внешними SPII или FPGA EPROM интерфейсами. В режиме FPGA EPROM после включения питания конфигурация из EPROM будет автоматически загружена в FPAA, и устройство сразу же начнет работать.